Einnovior offers a wide array of Signal Integrity Analysis Services. A growing number of companies are experiencing a sharp upturn in system-level Signal Integrity issues that result in project delays and increased cost. We are capable of supporting for a quick turn design analysis services.

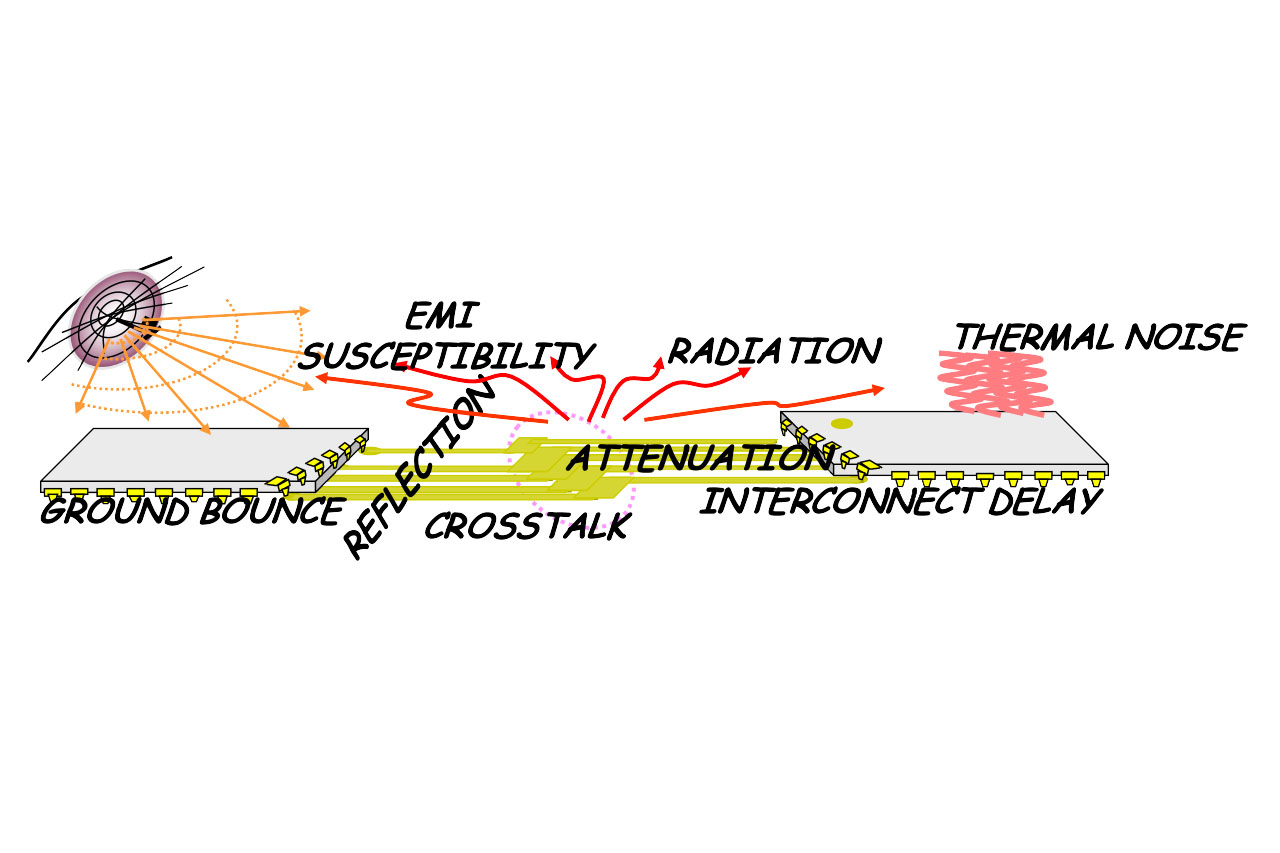

Rise time becoming more rapid (bandwidth increasing)

Controlled Impedance

Reflection and Ringing

Crosstalk

Skew

Loss

Dispersive effects (skin effect, dielectric losses)

Lower power-supply voltage and High current

Power supply droop and ground bounce

Adequate power plane decoupling is the key

Power delivery impedance is frequency dependent

Common-mode radiated noise (EMI)

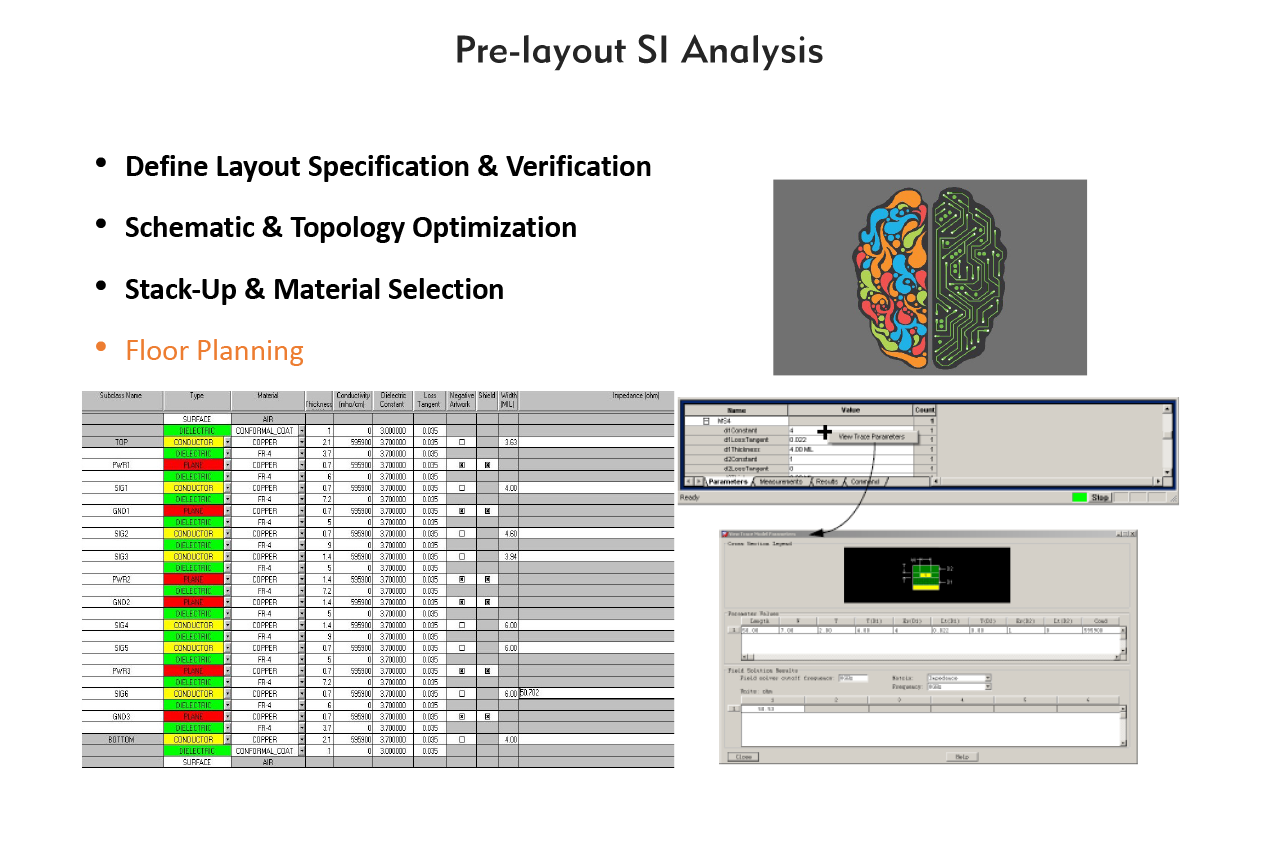

SI Analysis Advantage

By Including SI Analysis in Design flow, there are more chances for first time success

Avoid “trial and error” design method based on prototype iteration

Avoid taking the risk of poor production yield, worse and unreliable operation

Good Signal Integrity

Einnovior offers a wide array of Signal Integrity Analysis Services. A growing number of companies are experiencing a sharp upturn in system-level Signal Integrity issues that result in project delays and increased cost. We are capable of supporting for a quick turn design analysis services.

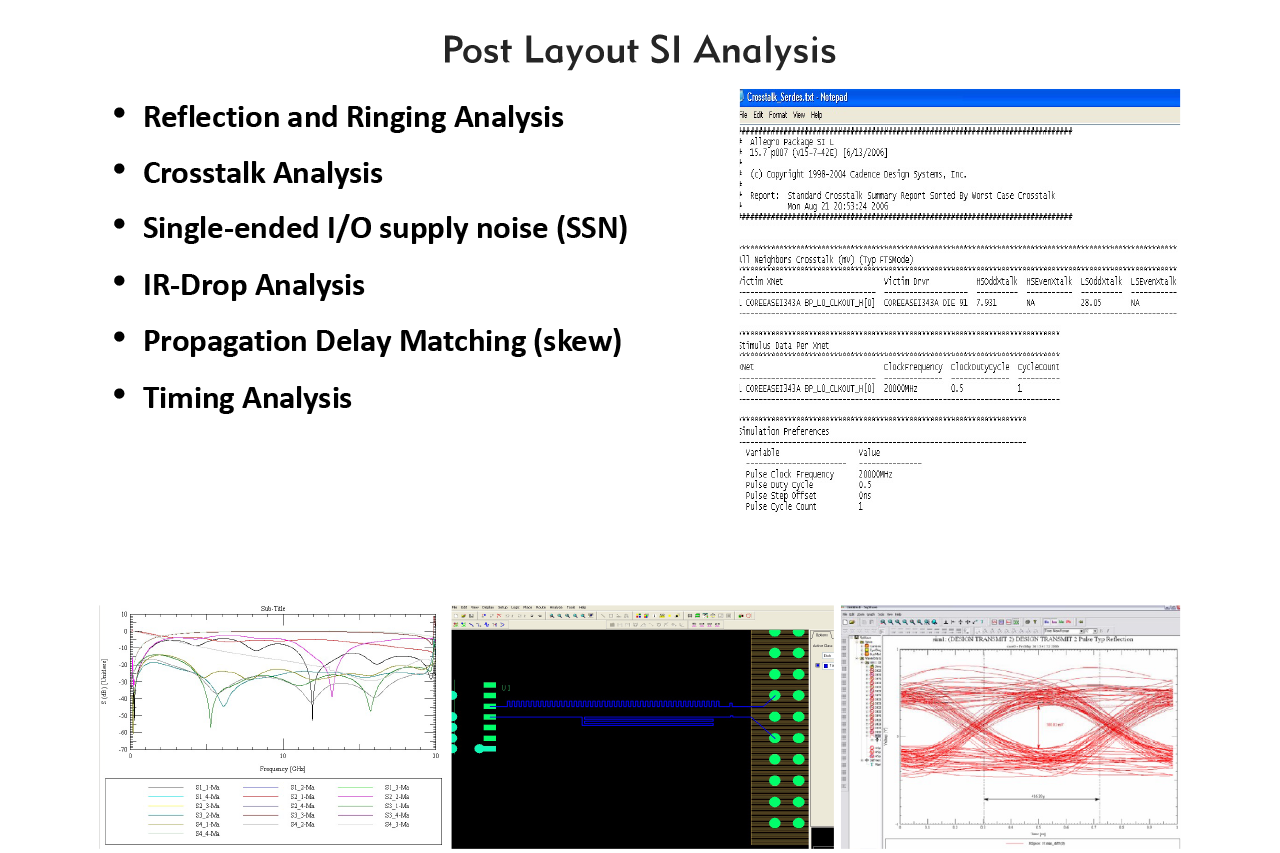

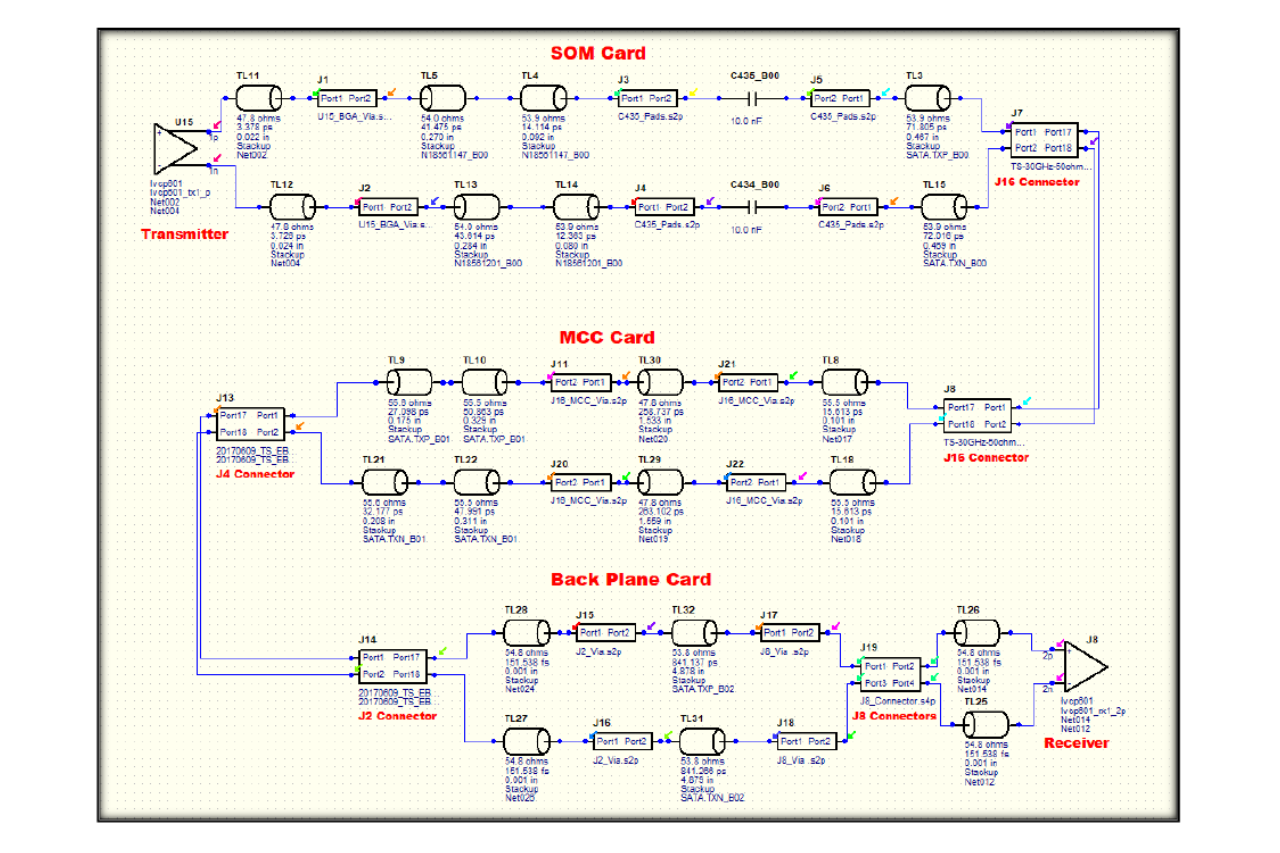

The scope of work is to carry out Multi-board Post layout Serdes simulations of SATA interface for the boards MCC, SOM & backplane. The details for SI requirement were received and based on this proposal has been prepared.

The requirement is to carry out as described below:

Post layout SI simulations for SATA transmitter pair running at 3 Gbps per pair from TMS(U15) From SOM Card to MCC Card to Backplane Card Connector J8

Post layout SI simulations for SATA receiver pair running at 3 Gbps per pair from J8 Connector Backplane Card to MCC to SOM TMS(U15) Processor

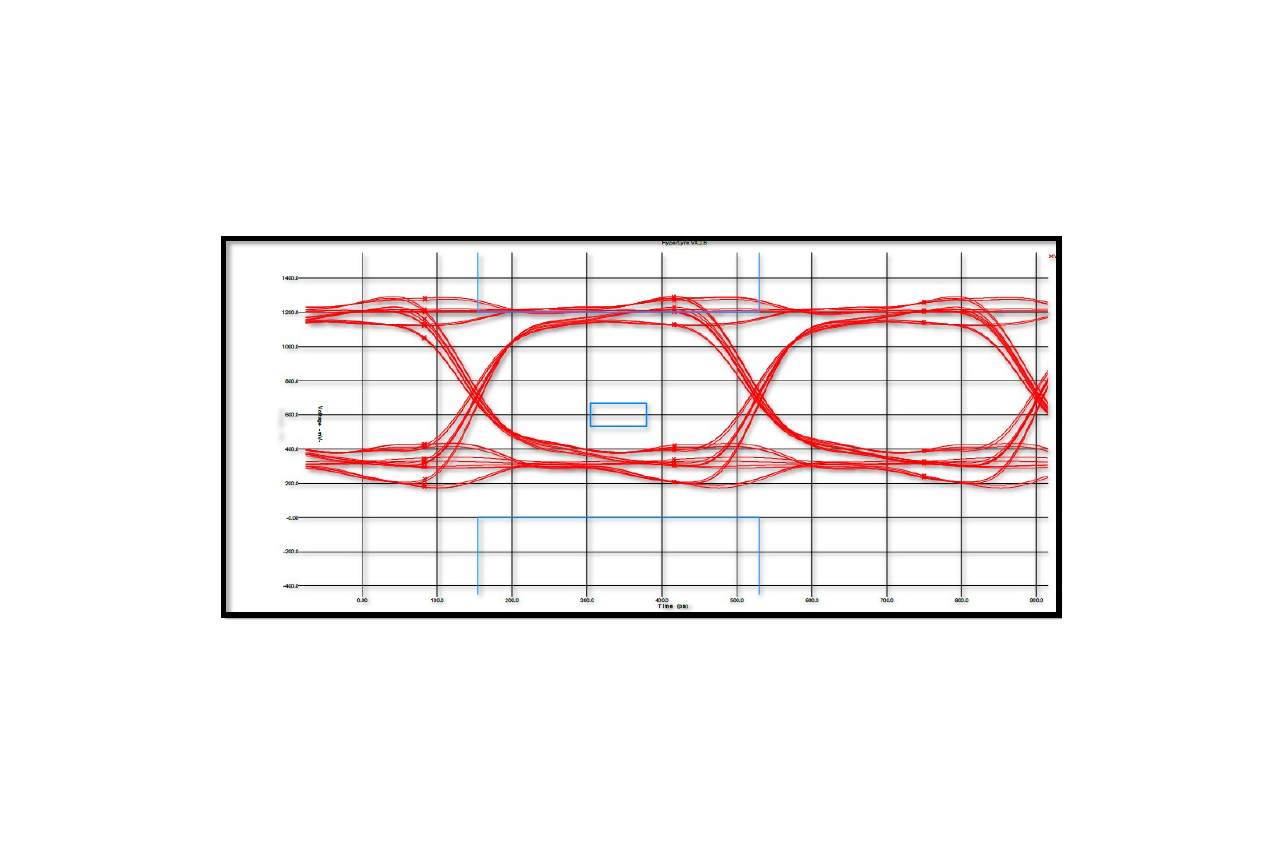

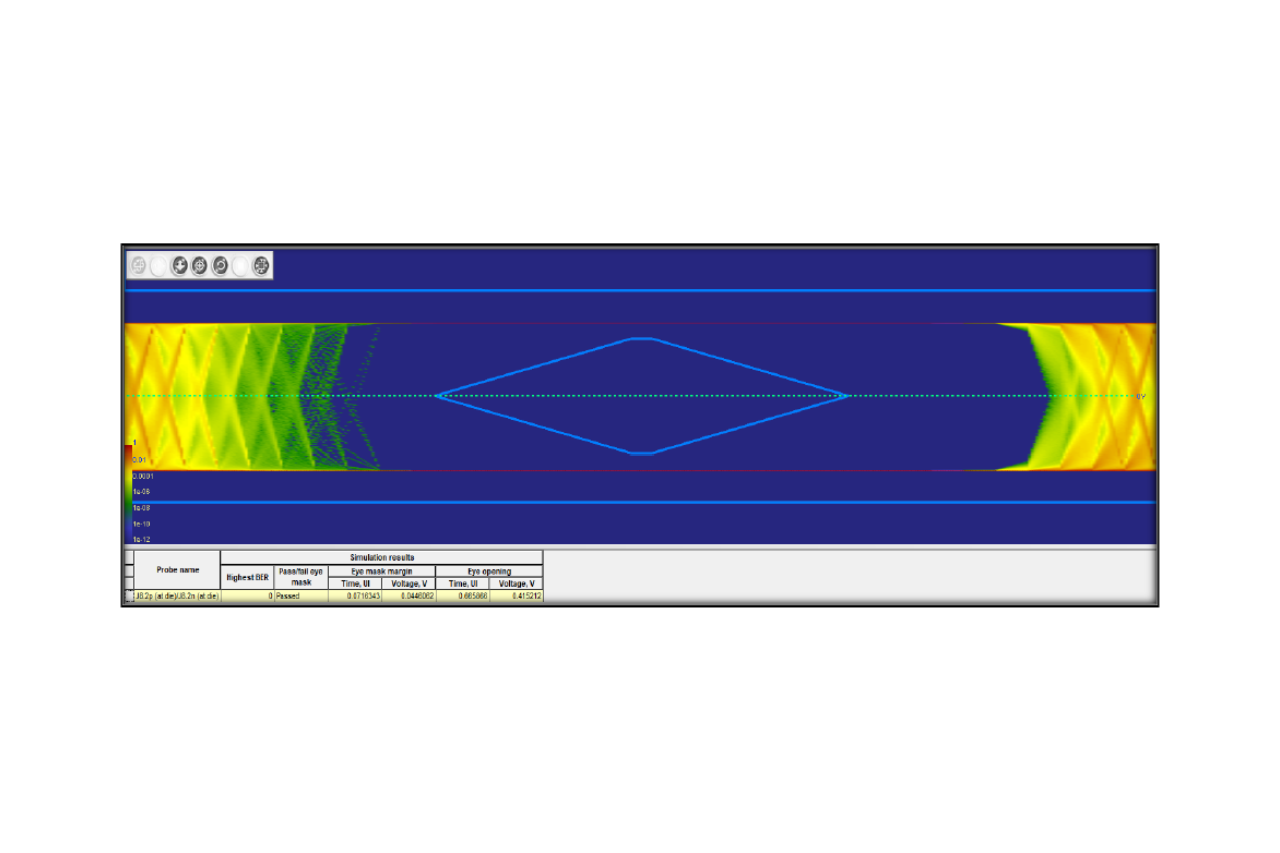

Eye Density Plot - Observations

From the above figure, it can be observed that the eye density plot satisfies with the eye mask requirements. Simulation results as per SATA Standard Specifications

Einnovior offers a wide array of Signal Integrity Analysis Services. A growing number of companies are experiencing a sharp upturn in system-level Signal Integrity issues that result in project delays and increased cost. We are capable of supporting for a quick turn design analysis services.

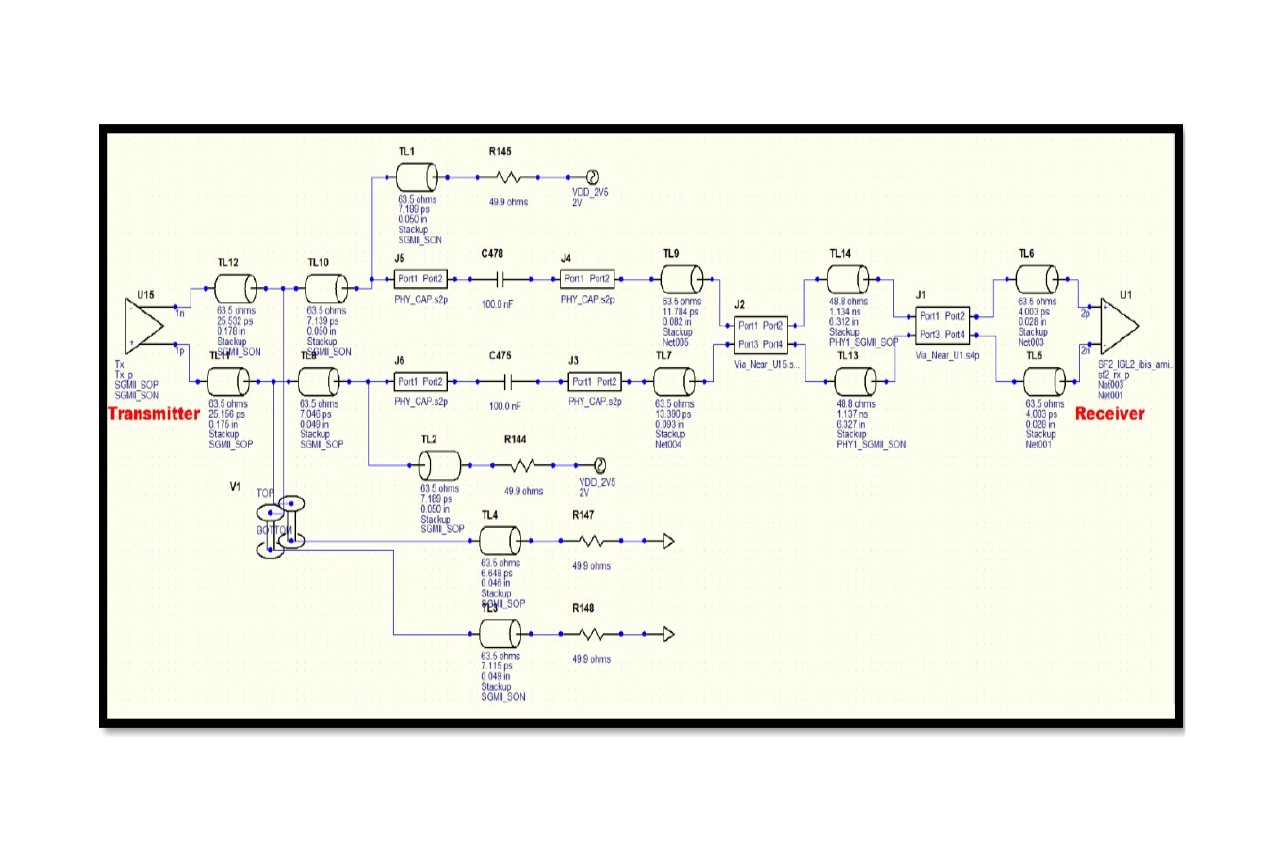

The scope of work is to carry out Multi-board Post layout Serdes simulations of SGMII interface for ABCM board. The details for SI requirement were received and based on this proposal has been prepared.

The requirement is to carry out as described below:

Post layout SI simulations for SGMII transmitter pair running at 1.25 Gbps per pair from U1 to U15

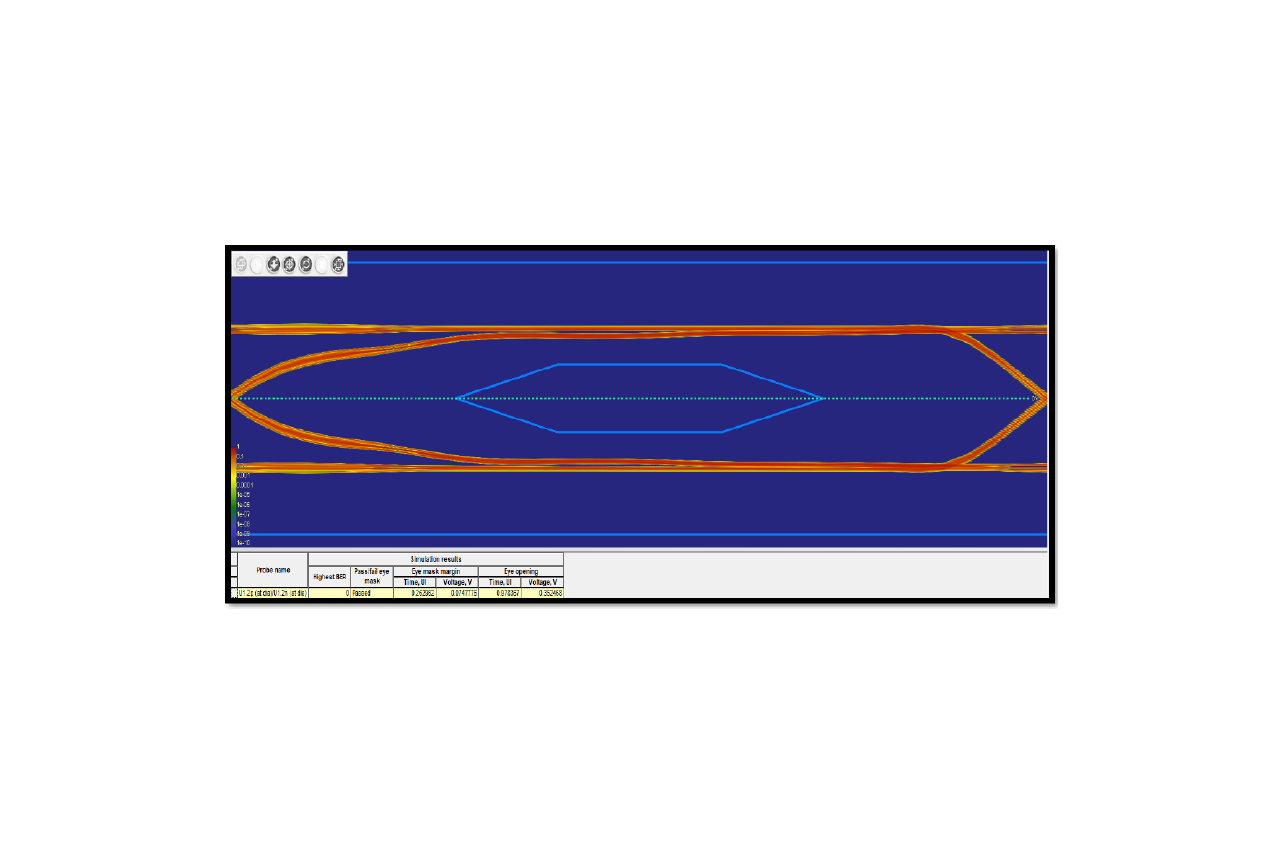

Eye Density Plot - Observations

From the above figure, it can be observed that the eye density plot satisfies with the eye mask requirements. Simulation results as per SGMII Standard Specifications.

Einnovior offers a wide array of Signal Integrity Analysis Services. A growing number of companies are experiencing a sharp upturn in system-level Signal Integrity issues that result in project delays and increased cost. We are capable of supporting for a quick turn design analysis services.

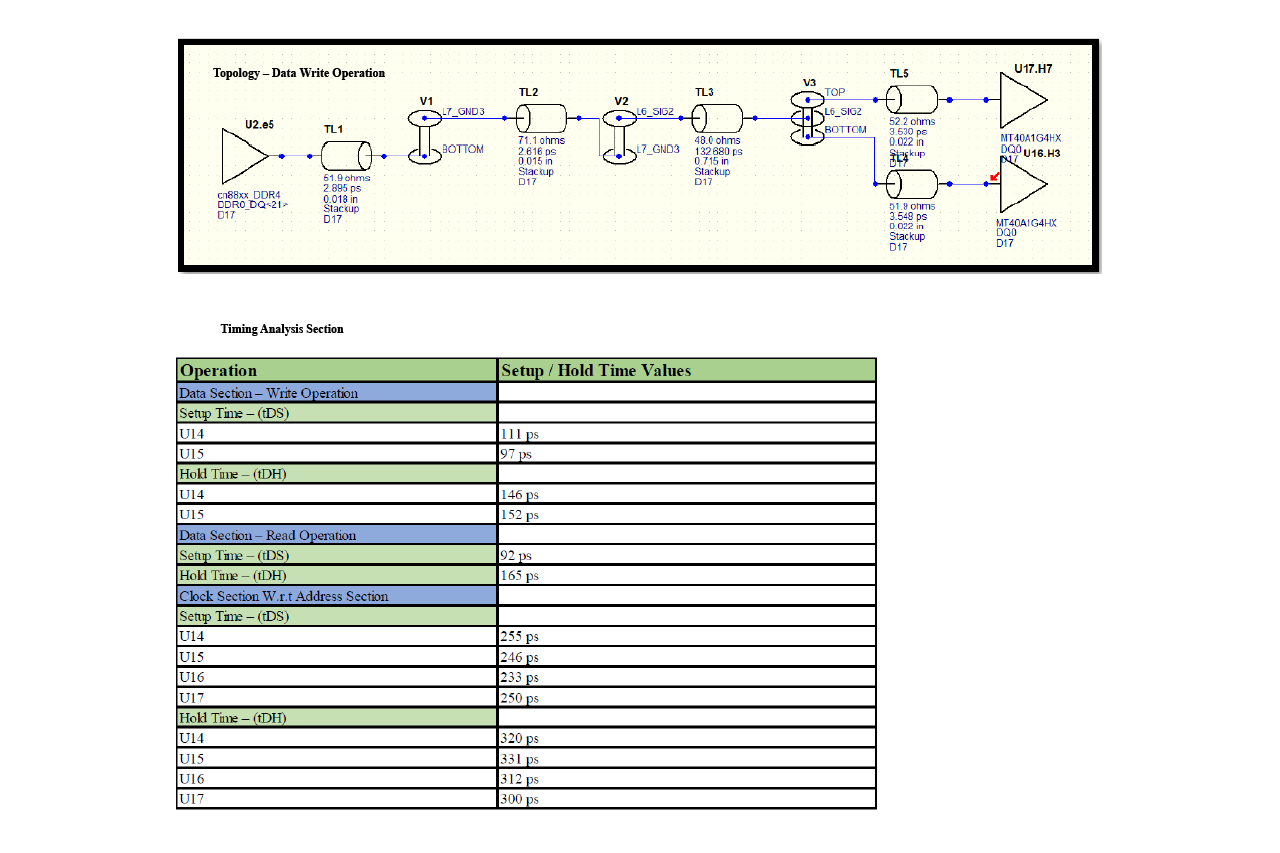

The scope of work is to carry out Post layout SI simulations for DDR4 Section for the given critical signal for the board SASB-Proto.brd. The details for SI requirement were received and based on this proposal has been prepared.

The requirement is to carry out SI Analysis for the given signal list as described below:

Data Section , Address Section , Clock Section , Timing Analysis

Eye Density Plot - Write Operation

From the above eye diagram’s, it can be observed that the waveforms at the receiver satisfies the threshold requirements. With the model used at the receiver & model used at the Controller.